16-битные микроконтроллеры Microchip

Архитектура

Ядро dsPIC/PIC24 построено по модифицированной Гарвардской архитектуре с расширенной системой команд. Архитектура dsPIC/PIC24 не является какой-либо модификацией привычных для разработчиков 8-битных ядер Microchip (Baseline, Midrange, PIC18) – это абсолютно новая разработка.

Микроконтроллеры dsPIC30/33 поддерживают выполнение специфических для алгоритмов цифровой обработки сигналов инструкций (умножение с накоплением), специальные методы адресации (модульная, бит-реверсивная). Все 16-битные контроллеры имеют векторную приоритетную систему прерываний, возможность отображения части программной памяти в нереализованную на кристалле область ОЗУ, знаковые вычисления с целыми числами и числами с фиксированной точкой. Более подробно особенности архитектуры 16-битных микроконтроллеров Microchip будут рассмотрены в этой части статьи.

В качестве примера рассмотрим структуру программной памяти, памяти данных, системы прерываний, АЛУ и набора инструкций микроконтроллеров dsPIC30, указав существенные отличия для других 16-битных семейств.

Организация памяти программ и памяти данных

Память программ

Карта памяти программ всех контроллеров dsPIC/PIC24 линейная и несегментированная. Все инструкции имеют фиксированную длину 24-бита; счетчик инструкций – 23-битный, младший бит всегда равен 0 для обеспечения выравнивания данных при выборке инструкции. Таким образом, эффективное количество адресуемых инструкций равно 222 ~ 4 млн.

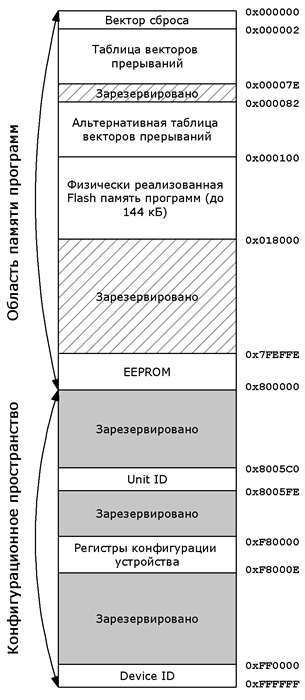

Карта программной памяти микроконтроллера dsPIC30F6014 изображена на рис. 1. Адрес 0x00 является вектором сброса. Далее расположена основная и альтернативная таблица векторов прерываний – эти области программной памяти будут более подробно рассмотрены в соответствующем разделе статьи. Следующая область – область пользовательской программы, объем этого сектора зависит от объема интегрированной Flash-памяти.

Рис. 1. Карта памяти программ микроконтроллера dsPIC30F6014 (не в реальном масштабе)

Микроконтроллеры семейства dsPIC30 имеют интегрированную память EEPROM, которая отображена в соответствующий сектор программной памяти. Семейства dsPIC33, PIC24F/H не имеют EEPROM, что связано с изменением технологии изготовления кристаллов. Поэтому при необходимости наличия в системе энергонезависимой памяти малого объема с большим количеством циклов перепрограммирования рекомендуется использовать внешние микросхемы памяти EEPROM с последовательным интерфейсом.

Половину карты программной памяти занимает так называемое «конфигурационное пространство». Во всех 16-битных микроконтроллерах физически реализована только небольшая часть этого сектора – это слова конфигурации, определяющие режим работы контроллера после сброса и идентификационный код кристалла, предназначенный для определения контроллера аппаратными средствами разработки.

Физически программная память во всех контроллерах 16-битного семейства реализована в виде перепрограммируемой Flash-памяти. Все контроллеры поддерживают внутрисхемное программирование и программирование в ходе выполнения программы.

В ходе выполнения программы существует три способа доступа к программной памяти:

- Выборка инструкции в соответствии со значением командного счетчика – собственно само выполнение программы.

- Использование инструкций табличного чтения-записи, позволяющее получить доступ как к слову (16-бит), так и к байту программной памяти. Табличная запись осуществляется через буфер, не отображаемый в ОЗУ. Для контроллеров dsPIC30 минимальный объем записываемых данных равен 12 байтам (4 программных слова, 1/8 сектора Flash памяти), для контроллеров dsPIC33 и PIC24F/H – 192 байта (64 программных слова – один сектор Flash памяти).

- Чтение программной памяти с помощью механизма PSV (Program Space Visibility) - отображения сектора памяти программ в область ОЗУ. Механизм PSV позволяет отобразить любую часть программной памяти объемом 32 кБайта в верхнюю, не реализованную физически область ОЗУ (рис. 2). PSV предоставляет уникальную возможность обращаться к младшим 16-битам программного слова как к динамическим данным - любые инструкции осуществляющие чтение из ОЗУ могут использовать программную память в качестве источника. Механизм PSV применяется, если алгоритм содержит большие массивы констант: текстовые строки, коэффициенты цифровых фильтров и т. п.

Существенное отличие DSC dsPIC30 и остальных 16-битных семейств (dsPIC33, PIC24F/H) заключается в технологии изготовления интегрированной Flash-памяти. Как следствие – различное количество циклов перепрограммирования. Для dsPIC30 оно составляет 100 тыс., для dsPIC33 и PIC24F/H – всего 1 тыс. Может показаться, что это серьезный недостаток новых контроллеров, однако как показывает практика 1 тысячи циклов перезаписи достаточно для большинства задач, в том числе и для реализации калибруемых устройств.

Различная технология изготовления кристалла определяет и различие в спецификации программирования – микроконтроллеры dsPIC33 и PIC24F/H не требуют подачи высокого напряжения (13 В) на кристалл во время программирования. Кроме того, значительно увеличилась скорость операций с памятью – для контроллеров с объемом Flash 64 кБ полный цикл стирание-запись занимает менее 1 секунды.

Память данных

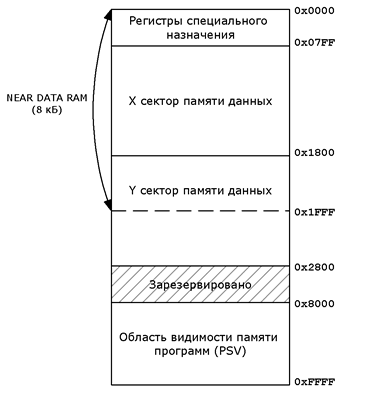

Шина адреса данных микроконтроллеров dsPIC30/33 и PIC24F/H позволяет адресовать до 64 кБ памяти ОЗУ, которая физически выполнена в качестве статической памяти с возможностью байтового доступа. Почти все инструкции, работающие с ОЗУ, имеют спецификатор, указывающий, будет ли осуществляться доступ к слову (16-бит) или к байту. Карта памяти данных микроконтроллера dsPIC30F6014 приведена на рис. 2.

Рис. 2. Карта памяти данных микроконтроллера dsPIC30F6014 (не в реальном масштабе)

В начале ОЗУ расположена область регистров специального назначения (SFR) объемом 2 кБайта. Внутри семейства все регистры SFR расположены статически по одним адресам.

С адреса 0x800 начинается сектор ОЗУ общего назначения, максимальный объем которого составляет 30 кБайт; в разных контроллерах только часть этого сектора может быть реализована физически. Верхнюю половину ОЗУ занимает область, в которую отображается часть программной памяти при использовании механизма PSV.

В семействах с DSP-ядром (dsPIC30/33) реализовано два адресных генератора, что позволяет инструкциям DSP-ядра делать две выборки из ОЗУ за один командный такт. Это объясняет разделение области ОЗУ общего назначения на два сектора X и Y (см. рис. 2). Однако это разделение не является сегментированием или ограничением – для всех инструкций CPU-ядра сектор ОЗУ общего назначения линеен.

Первые 8 кБайт ОЗУ (включая область SFR) называются пространством ближней памяти (Near Data Space). Прямая адресация возможна только к этому сегменту. Остальная часть ОЗУ может быть адресована косвенно.

16-битная архитектура Microchip предусматривает использование программного стека, указателем на который является один из рабочих (work) регистров. Стек растет с увеличением указателя, при этом возможен аппаратный контроль переполнения и опустошения стека. В случае переполнения или опустошения стека, ядром процессора генерируется аппаратное исключение – специальный вид прерывания который будет рассмотрен в пункте «Система прерываний» данной статьи. Размер стека определяется программно.

При вызове подпрограммы в стек заносится адрес возврата и часть регистра статуса. Указатель на стек может быть изменен программно, что позволяет реализовывать гибкие системы реального времени.

В 16-битном ядре так же присутствует LINK-регистр, который позволяет выделять в стеке фрейм для локальных переменных функции. Процедуры выделения и сброса фрейма выполняются программно за один командный такт.

АЛУ, умножитель, поддержка деления

16-битное арифметико-логическое устройство (АЛУ) позволяет выполнять за один командный такт следующие операции: сложение, вычитание, битовый сдвиг и поразрядные логические операции, включая инверсию. Результаты операций влияют на статусные флаги. АЛУ выполняет операции с 16-битными словами или байтами в зависимости от синтаксиса инструкции.

В состав ядра входит умножитель 17 x 17 бит, который позволяет выполнять операции умножения 16 x 16, 16 x 8 и 8 x 8 бит, знаковые, беззнаковые и смешанные за один командный такт. При знаковом и смешанном умножении используется расширение знака. Операции умножения не влияют на статусные флаги. В качестве операндов используются рабочие регистры, результат умножения возвращается в указанную регистровую пару.

Аппаратная поддержка деления (итерационный метод) позволяет значительно сократить время выполнения математических алгоритмов. Операции деления 32/16 и 16/16 бит (знаковые и беззнаковые) выполняются за 18 командных тактов. В качестве операндов используются рабочие регистры, после выполнения деления доступен результат и остаток.

Ядро содержит модуль сдвига (barrel shifter), который позволяет выполнять за один командный такт операции сдвига и вращения на произвольное (до 15) количество бит. Сдвиг вправо может быть логическим (без расширения знака) или арифметическим (с расширением знака).

Ядро ЦОС

Ядро цифровой обработки сигналов (ЦОС) является независимым от CPU-ядра вычислительным модулем, который присутствует только в контроллерах семейства dsPIC30 и dsPIC33.

Умножитель dsPIC30/33 позволяет выполнять знаковые и беззнаковые операции с данными формата Q.31 (фиксированная точка). Тип операндов определяется битом в служебном регистре CORCON. При умножении чисел с фиксированной точкой производится сдвиг результата влево на один бит, что позволяет сохранить формат числа, при этом младший бит результата всегда обнуляется. Делитель микроконтроллеров с DSP ядром так же позволяет выполнять знаковое деление чисел в формате Q.31.

Следует заметить, что умножитель и делитель могут использоваться как стандартными инструкциями умножения и деления, так и инструкциями DSP ядра, операционный код которых отличается от стандартных. Так, например, инструкция MUL является стандартной инструкцией умножения CPU-ядра (для нее доступны функции умножителя, указанные в предыдущем разделе), а инструкция MPY – инструкцией умножения DSP ядра, с помощью которой можно производить операции с Q.31 числами.

Результат инструкций DSP-ядра всегда сохраняется в один из 40-битных аккумуляторов: ACCA или ACCB. Аккумуляторы отображены в ОЗУ и могут быть доступны для любых инструкций. При представлении чисел в виде Q.31 диапазон значений аккумулятора составляет [-256.0 , +256.0 - 2-31]. Аккумуляторы имеют статусные флаги, сигнализирующие о переполнении, частичном переполнении (результат по модулю больше 1.0), опционально установка этих флагов может генерировать прерывание. Содержимое 40-битного аккумулятора может сохраняться в 16-битном слове ОЗУ, при этом используются различные режимы округления и усечение.

Инструкции, поддерживаемые ядром DSP приведены в таблице 2.

Таблица 2. Инструкции, поддерживаемые DSP ядром

| DSP инструкция | Алгебраический эквивалент | Выполняемая операция |

|---|---|---|

| mac | a = a + b*c | Умножение двух операндов, добавление результата к аккумулятору |

| msc | a = a – b*c | Умножение двух операндов, вычитание результата из аккумулятора |

| mpy | a = b*c | Умножение двух операндов, сохранение результата в аккумулятор |

| mpy.n | a = -b*c | Умножение двух операндов, инверсия, сохранение результата в аккумулятор |

| ed | a = (b – c)2 | Вычисление евклидовой метрики, сохранение результата в аккумулятор |

| edac | a = a + (b – c)2 | Вычисление евклидовой метрики, добавление результата к аккумулятору |

В качестве примера рассмотрим одну из основных инструкций для ЦОС алгоритмов – инструкцию MAC – умножение с накоплением. Типовое использование MAC инструкции (ассемблер ASM30):

mac w4*w5, A, [w8]+=2, w4, [w10]-=2, w5, [w13]+=2

Данная запись означает следующее:

- значение

w4умножается на значениеw5, результат умножения добавляется к аккумуляторуACCA; - регистр

w4загружается значением по указателю W8 (указатель должен указывать на адрес в сегменте X ОЗУ); - указатель

w8увеличивается на 2; - регистр

w5загружается значением по указателюw10(указатель должен указывать на адрес в сегменте Y ОЗУ); - указатель

w10уменьшается на 2; - значение аккумулятора

ACCBсохраняется по указателюw13; - указатель

w13увеличивается на 2.

Все перечисленные операции с данными выполняются за один командный такт. Одновременная выборка операндов в ходе выполнения умножения вместе с аппаратными циклами do и repeat позволяет чрезвычайно эффективно реализовывать ЦОС алгоритмы.

К ядру ЦОС можно отнести два аппаратных цикла, do и repeat, хотя цикл repeat присутствует и в 16-битных контроллерах без DSP-ядра.

Цикл repeat позволяет аппаратно повторять (до 214 раз) выполнение одной инструкции. Аппаратная вложенность не поддерживается, однако программно может быть реализовано любое количество уровней – при этом необходимо сохранять счетчик цикла в стеке. Цикл repeat может использоваться, например, совместно с инструкцией mac, что позволяет всего двумя командами реализовать вычисление КИХ фильтра.

Цикл do предназначен для повторения блока кода объемом до 216 инструкций. Произвольный блок может быть выполнен циклически до 214 раз. Цикл do аппаратно поддерживает 7 уровней вложенности, программно может быть реализовано произвольное количество уровней. Выполнение цикла может быть досрочно прервано в любой момент. Цикл do можно использовать для выполнения операций двумерной фильтрации, работы с векторами и матрицами, и т. д.

Кроме ЦОС инструкций, DSP-ядро аппаратно поддерживает специфические для ЦОС алгоритмов методы адресации. К таким относятся адресация по модулю и бит-реверсивная адресация.

Механизм адресации по модулю выполняется отдельно для областей ОЗУ X и Y и позволяет эффективно реализовывать циклические буферы. Суть адресации по модулю состоит в том, что контроль выхода указателя за пределы буфера и его возврат на начало осуществляются аппаратно. При этом максимально возможный размер буфера составляет 215 слов ОЗУ, а размер буфера не обязательно должен быть кратен степени 2. Возможен опрос буфера как с увеличением, так и с уменьшением указателя.

Бит-реверсивная адресация является одной из основных операций алгоритма БПФ (быстрое преобразование Фурье) с прореживанием по времени или частоте. В DSP-ядре микроконтроллеров dsPIC30/33 реализована бит-реверсивная адресация, позволяющая выполнять БПФ с буфером, размер которого кратен степени 2 (radix-2 FFT). Суть метода заключается в зеркальном отражении части разрядов адреса для выборки следующего элемента из буфера, максимальный объем которого равен 215 (32768) 16-битных слов.

DMA

Контроллер DMA (Direct Memory Access – прямой доступ к памяти) является частью ядра семейств PIC24H и dsPIC33. В PIC24F и dsPIC30 контроллер DMA отсутствует. Назначение DMA – аппаратная поддержка обмена данными между периферией и областью ОЗУ общего назначения.

Контроллер DMA имеет 8 однонаправленных каналов, каждый из которых может обслуживать любой, поддерживающий аппаратный обмен периферийный модуль. К таким модулям относятся: модули захвата, модули сравнения, таймеры, SPI, UART, CAN, АЦП, DCI. Контроллер имеет 2 кБайт двухпортовой памяти ОЗУ, которая может использоваться в качестве буфера DMA.

Контроллер DMA и ядро микроконтроллера могут получать одновременный доступ как к двупортовому буферу, так и к регистрам периферийного модуля. Единственное ограничение – DMA и CPU ядро не должны одновременно сохранять данные по одному адресу. В этом случае приоритет имеет CPU ядро, а контроллер DMA генерирует аппаратное исключение – специальный вид прерывания который будет рассмотрен в пункте «Система прерываний» данной статьи.

Контроллер DMA поддерживает следующие режимы работы:

- однократный обмен (one-shot). В этом режиме контроллер DMA завершает работу после одной передачи данных, генерируя при этом прерывание. Для продолжения работы канал DMA нужно переинициализировать.

- обмен с автоматическим повтором (auto-repeat) подразумевает автоматическую переинициализацию канала DMA после завершения сессии обмена – указатель на буфер DMA сбрасывается, генерируется прерывание.

- прерывание при половинной передаче (half buffer transfer interrupt). В этом случае DMA контроллер генерирует прерывание при половинном заполнении буфера. Это позволяет начать обработку данных еще до завершения сессии обмена. При заполнении буфера канал DMA переинициализируется автоматически, прерывание при этом не генерируется.

- режим «ping-pong». Канал DMA использует два буфера. При заполнении первого буфера указатель перемещается на начало второго, генерируется прерывание. После заполнения второго буфера указатель перемещается на начало первого, генерируется прерывание. Это позволяет CPU-ядру работать с данными в одном буфере, в то время как DMA контроллер заполняет другой.

- режим косвенной адресации периферии. В этом режиме указатель на буфер генерирует не DMA контроллер, а непосредственно, поддерживающий этот режим, периферийный модуль (к таким относятся модули CAN и АЦП). Например, модуль АЦП может быть настроен так, чтобы отсчеты разных каналов АЦП сохранялись в определенных областях DMA буфера, вне зависимости от последовательности преобразования.

Набор инструкций и методы адресации

16-битная архитектура Microchip имеет в своем составе блок из 16 рабочих регистров w0…w15. Все регистры ортогональны с точки зрения системы команд, то есть могут быть использованы в качестве операнда инструкции. Часть регистров имеют служебные функции: w15 – это указатель стека, w14 – указатель стекового фрейма. Некоторые инструкции могут использовать в качестве операндов или регистров сохранения результата только определенный w-регистр или регистровую пару.

16-битные микроконтроллеры Microchip имеют расширенный набор инструкций, большинство из которых поддерживает операции типа «чтение-модификация-запись», что позволяет работать с данными напрямую в ОЗУ, не используя рабочие регистры. Большинство инструкций являются трехоперандными (A = B + C) и могут работать как с байтами, так и с 16-битными словами.

Семейства с DSP-ядром (dsPIC30/33) имеют 83 инструкции (включая инструкции DSP-ядра), семейства без DSP-ядра (PIC24F/H) – 76. Все инструкции выполняются за один командный такт за исключением:

- инструкций изменения программного потока – 2 или 3 такта,

- инструкций табличного чтения/записи – 2 такта,

- инструкции

mov.d– 2 такта, - инструкции

do– 2 такта.

Все инструкции можно условно разделить на несколько групп:

MOVE– инструкции перемещения данных;MATH– инструкции выполнения математических операций;LOGIC– инструкции выполнения поразрядных логических операций;SHIFT/ROTATE– инструкции сдвига с переносом и без переноса;BIT– инструкции работы с битами;STACK– инструкции работы со стеком;PROGRAMM FLOW– инструкции изменения программного потока (переходы, вызовы, условные переходы);CONTROL– инструкции управления ядром (инициализация аппаратных циклов, программный сброс, перевод контроллера в энергосберегающий режим);DSP– инструкции DSP-ядра, присутствуют только в системе команд контроллеров dsPIC30/33.

Архитектура поддерживает большое количество методов адресации:

- прямая адресация, адрес операнда указывается непосредственно в операционном слове инструкции. Операнд должен быть расположен в области Near Space (первые 8 кБайт ОЗУ, рис. 2):

add 0x900, w0 ;Сложение значения по адресу 0x900 с w0. Результат сохраняется в w0

- расширенный режим инструкции

mov– прямая адресация, но может адресоваться вся память ОЗУ

mov 0x2500, w7 ;Сохранение значения по адресу 0x2500 в регистр w7

- прямая адресация регистров. В качестве операндов используются значения рабочих регистров:

ior w0, w2, w5 ;Поразрядное логическое ИЛИ регистров w0 и w2, сохранение результата в w5

- косвенная адресация – может использоваться в большинстве инструкций:

add w4, [w5], [w6] ;Сложение W4 со словом по указателю W5, сохранение результата по указателю W6

- косвенная адресация с пре/пост инкрементом и декрементом, при этом учитываются правила адресной арифметики в зависимости от типа операнда (байт или слово):

mov [++w0], [w1--] ;Увеличение указателя w0 на 2, перемещение значения по указателю w0 в ячейку, на которую указывает w1, уменьшение указателя w1 на 2.

- косвенная адресация со смещением:

mov [w4+w5], [w6++] ;Получение указателя на ячейку операнда, путем сложения w4 и w5, перемещение значения по полученному указателю по адресу w6, увеличение значения w6 на 2

Поддержка различных методов адресации позволяет получать очень компактный код при использовании компиляторов с языков высокого уровня. Следует так же отметить возможность вызова и перехода по значению в регистре (аналог вызова функции по указателю в Си) и инструкцию запрещения прерываний на определенное количество командных тактов (позволяет выполнять набор инструкций как одну атомарную).

Система прерываний

Микроконтроллеры dsPIC30/33 и PIC24F/H имеют векторную приоритетную систему прерываний. Каждый источник прерывания имеет собственный вектор в таблице, расположенной в программной памяти. Внутри таблицы прерывания имеют естественный приоритет: при одновременном возникновении двух прерываний приоритет имеет то, чей вектор имеет меньший адрес. Вектора представляют собой 24-битное слово программы, в котором должна быть расположена команда перехода на сервис обработчика прерывания.

Пользователь может изменить естественный приоритет, назначив источнику прерывания искусственный приоритет. Для того чтобы прерывание было сгенерировано, необходимо, чтобы назначенный приоритет был выше текущего приоритета ядра (который так же можно изменять программно). При возникновении прерывания в программный счетчик записывается адрес вектора прерывания, а приоритет CPU-ядра становится равным приоритету возникшего прерывания. Это позволяет организовывать гибкую систему вложенных прерываний.

Возможно назначение приоритета каждому прерыванию, количество возможных уровней приоритета равно 8. CPU ядро может иметь приоритет от 0 до 15, уровни 8 – 15 зарезервированы для аппаратных исключений.

Аппаратные исключения – это определенный вид немаскируемых прерываний, которые генерирует CPU-ядро. Условно исключения можно разделить на программные и аппаратные.

К программным относятся исключения, которые позволяют продолжить выполнение работы после программного сброса флага исключения. Программные исключения имеют приоритет от 8 до 12. К программным исключениям относятся: исключение АЛУ (которое генерируется ядром, например, при делении на 0) и ошибка стека.

При возникновении аппаратного исключения программа не может продолжить работу до тех пор, пока ошибка, которая вызвала исключение, не будет устранена – флаг аппаратного исключения не может быть сброшен программно. Аппаратные исключения имеют приоритет от 13 до 15. К аппаратным исключения относятся: ошибка адреса (не выровненный доступ к памяти программ или памяти данных) и ошибка тактового генератора (нестабильная работа PLL, отсутствие внешней тактовой частоты).

Система прерываний имеет фиксированное время реакции – 5 командных тактов. Возврат из прерывания осуществляется за 3 командных такта. Следует заметить, что при входе в прерывание часть статус-регистра SR автоматически сохраняется в стеке, это позволяет уменьшить объем кода и время выполнения обработчика прерывания. Все флаги прерываний устанавливаются вне зависимости от того, разрешено прерывание или нет.

В программной памяти расположены две идентичные таблицы прерываний (рис. 1) – основная и альтернативная. Используемая в текущий момент таблица прерываний может быть выбрана программно. Это удобно, например, для реализации внутрисхемного программного загрузчика (bootloader).

Микроконтроллеры семейства dsPIC30 имеют 54 вектора прерывания и 8 векторов исключений в каждой таблице. Семейства dsPIC33 и PIC24F/H имеют расширенные таблицы прерываний – 118 векторов прерываний и 8 векторов исключений.

Служебные модули

Система тактирования

Как и в 8-битных контроллерах Microchip, в семействе dsPIC30 команда выполняется за 4 такта генератора, то есть, для достижения максимальной производительности 30 MIPS тактовая частота должна быть равна 120 МГц.

Семейства PIC24F/H и dsPIC33 имеют переработанную схему конвейера – это первые контроллеры Microchip, в которых команда выполняется за 2 (!) такта генератора. Максимальная производительность PIC24F составляет 16 MIPS (тактовая частота 32 МГц), PIC24H/dsPIC33 – 40 MIPS (тактовая частота 80 MHz). Значительное увеличение производительности по сравнению с dsPIC30 связано с использованием более «тонкого» техпроцесса изготовления кристаллов – 0,25 мкм.

16-битные семейства имеют три различных типа схемы тактирования:

dsPIC30

Схема тактирования имеет четыре источника – первичный кварцевый генератор (4-10 МГц), вторичный кварцевый генератор (32 кГц), внутренний RC генератор 8 МГц и внутренний низкочастотный RC генератор 512 кГц. Первичный генератор может тактировать схему умножения частоты с ФАПЧ (PLL), коэффициент умножения (4, 8, 16) выбирается в конфигурационном слове и не может быть изменен в ходе выполнения программы. PLL-умножитель не может быть подключен к внутренним RC генераторам или ко вторичному кварцевому генератору. Микроконтроллер может тактироваться от внешнего источника частоты (0-40 МГц). Система тактирования содержит детекторы стабильности тактовой частоты - возможно автоматическое переключение на вторичный источник при сбое первичного. Схема тактирования dsPIC30 содержит делитель тактовой частоты, подаваемой на ядро и периферию. Делитель имеет коэффициенты 1, 4, 16 и 64, коэффициент может быть изменен программно.

PIC24F

Схема тактирования почти полностью повторяет dsPIC30. Так как максимальная частота тактирования этого семейства составляет 32 МГц, внутренний PLL-умножитель имеет только один коэффициент умножения на 4. Внутренний прецизионный RC генератор 8 МГц может использовать PLL для умножения частоты (в отличие от dsPIC30), следовательно, можно получить максимальную производительность 16 MIPS, используя для тактирования внутренний генератор. Умножитель можно отключить программно. Важной особенностью является разделение линий тактирования ядра и периферии. Сигнал тактирования на ядро подается через программно управляемый делитель. Это предоставляет уникальную возможность уменьшения частоты тактирования ядра (что уменьшает потребление энергии) при сохранении частоты тактирования периферии (важно, например, для быстрых коммуникационных интерфейсов – SPI, UART и т. п.)

PIC24H/dsPIC33

Схема тактирования аналогична PIC24F, однако в ней полностью переработан PLL-умножитель. Опуская детали, можно сказать, что коэффициент умножения является дробным и настраивается программно. Таким образом, если контроллер тактируется от кварцевого резонатора 4 МГц, с помощью PLL можно получить сетку частот тактирования от 12,5 МГц до 80 МГц с шагом 0,25 МГц. Внутренний высокочастотный RC генератор в отличие от dsPIC30/PIC24F имеет частоту 7.37 МГц. Следует отметить, что во всех семействах частота внутреннего генератора может программно корректироваться в пределах +/- 12% c шагом в десятые доли процента.

Система сброса

Система сброса всех 16-битных микроконтроллеров Microchip идентична, за исключением того, что в 3-х вольтовых семействах dsPIC33 и PIC24F/H отсутствует сброс по снижению напряжения питания (BOR - Brown Out Reset). Это связано с тем, что максимальная частота тактирования базового семейства dsPIC30 зависит от напряжения питания - детектор снижения необходим, чтобы предотвратить некорректную работу системы. Контроллеры dsPIC33 и PIC24F/H обеспечивают максимальную производительность во всем диапазоне питающих напряжений, поэтому необходимость детектора BOR отсутствует. Источник сброса BOR заменен на сброс по снижению напряжения на выходе встроенного стабилизатора питания ядра.

Все семейства имеют следующие источники сброса:

- программный сброс – инструкция

reset; - внешний сброс по входу MCLR;

- сброс по переполнению сторожевого таймера;

- сброс по включению напряжения питания;

- сброс при конфликте исключений;

- сброс при неверном операционном коде инструкции (например, если программный счетчик указывает на область констант)

- сброс при использовании неинициализированных рабочих w-регистров

- сброс при неверном формате конфигурационного слова (только для PIC24F/H, dsPIC33).

При любом виде сброса все служебные регистры устанавливаются в определенное состояние, одинаковое для всех видов сброса. Исключения – регистр RCON (в котором находятся флаги системы сброса) и регистр управления схемой тактирования OSCCON.

Сторожевой таймер

Сторожевой таймер (WDT), как правило, используется для сброса контроллера в случае нарушения нормальной работы системы – сброс происходит при переполнении WDT. Сторожевой таймер тактируется от встроенного RC генератора, поэтому при правильном использовании WDT сброс произойдет даже в случае остановки всех источников тактирования.

В контроллерах dsPIC30 сторожевой таймер имеет два предделителя, позволяющих установить период таймера от 2 мс до 16 секунд. Работа таймера может быть разрешена программно.

В контроллерах PIC24F/H и dsPIC33 сторожевой таймер имеет предделитель и постделитель, позволяющие установить период таймера от 1 мс до 131 секунды, работа таймера может быть разрешена программно. Возможна работа WDT в оконном режиме - обнуление таймера необходимо производить в течение последней четверти его периода, в противном случае генерируется сброс контроллера.

Энергосберегающие режимы работы

Все 16-битные микроконтроллеры Microchip имеют два основных энергосберегающих режима:

SLEEP. В этом режиме останавливается источник тактирования (низкочастотный генератор, которым тактируется сторожевой таймер, продолжает работу), отключается ядро контроллера, отключаются все периферийные модули (кроме портов ввода-вывода, модулей внешнего прерывания и периферийных модулей, использующих внешнюю тактовую частоту) – это режим работы с самым низким потреблением. Вход в режим SLEEP осуществляется программно. Выход из режима осуществляется по внешнему прерыванию, событию сброса или по переполнению WDT.

IDLE. В этом режиме прекращается выполнение программы (изменение командного счетчика), но тактовый генератор и периферийные модули продолжают нормальное функционирование. Все периферийные модули имеют бит разрешения работы в режиме IDLE - возможно дополнительное снижение потребления путем отключения неиспользуемой периферии. Вход в режим осуществляется программно, выход – при возникновении любого немаскированного прерывания, сбросе контроллера или переполнении WDT.

Контроллеры семейств dsPIC33 и PIC24F/H имеют дополнительные функции, позволяющие значительно снизить потребление. Это режим DOZE и возможность полного отключения периферийных модулей.

Суть режима DOZE состоит в возможности уменьшения тактовой частоты, подаваемой на ядро контроллера, при неизменяемой частоте тактирования периферии. Делитель блока DOZE имеет коэффициенты деления от 1 до 1/128. Режим DOZE позволяет использовать полную пропускную способность коммуникационных интерфейсов или модулей генерации ШИМ при относительно низком общем потреблении кристалла.

Часть периферийных модулей имеет возможность полного отключения – все источники тактирования аппаратно отключаются, а служебные регистры модуля становятся недоступны. При этом периферийный модуль потребляет минимально возможный ток.

Система защиты кода CodeGuard™

Как и большинство присутствующих на рынке микроконтроллеров, 16-битные семейства Microchip имеют в своем составе схемы защиты кода от несанкционированного доступа (чтения или изменения). В 2006 году компания Micropchip анонсировала новую систему защиты кода CodeGuard™, которая используется во всех микроконтроллерах dsPIC33 и PIC24H.

В семействах PIC24F и в большинстве dsPIC30 используется стандартная схема – уровень защиты определяется двумя битами в слове конфигурации. Один из них запрещает чтение программной памяти через внешний интерфейс программирования, другой – запрещает запись в программную память. Последнее необходимо для защиты контроллера от записи заплатки, которая может, используя инструкции табличного чтения, передать код по последовательному интерфейсу.

Стандартная схема защиты ограничивает применение внутрисхемных загрузчиков, модулей дистанционного обновления прошивки, и т. д. Тем не менее, стандартная схема является одним из слоев защиты по спецификации CodeGuard™.

Система CodeGuard™ основана на следующих основных положениях:

- три уровня реализации: основной (Basic), аналогичный схеме защиты кода в PIC24F; промежуточный (Intermediate); продвинутый (Advanced).

- Flash память условно разбита на три сегмента:

- загрузочная область (Boot) – в которой может храниться код бутлоадера с поддержкой шифрования, ключи шифрования, данные идентификации прошивки, функции дешифровки и т. п.;

- защищенный сегмент (Secure) – в котором могут храниться функции, определяющие интеллектуальную стоимость устройства, таблицы, защищенные обработчики прерываний, и т. п.;

- основной сегмент (General) – в котором могут храниться драйверы периферии, большие таблицы данных, исполняемый код пользователя OEM продукции и т. п.

- каждый уровень реализации CodeGuard™ подразумевает разбивку Flash памяти на сегменты и их защиту. Для основного уровня CodeGuard™ существует только основной сегмент программной памяти, который может быть защищен. Для промежуточного уровня CodeGuard™ существуют основной и загрузочный сегменты. Для продвинутого уровня CodeGuard™ существуют все три сегмента: Boot, General и Secure.

- размеры сегментов Flash конфигурируются.

- в контроллерах dsPIC30, в которых реализована схема CodeGuard™ (dsPIC30F5011/13, dsPIC30F601xA, dsPIC30F6015, dsPIC30F1010, dsPIC30F202x), интегрированная память EEPROM так же может быть разбита на три сегмента аналогично Flash-памяти. При этом каждый сегмент Flash может использовать только соответствующий сегмент EEPROM.

- для каждого сегмента Flash доступно два уровня защиты:

- высокий (High) – программный доступ (инструкции вызова и перехода) возможен только в первые 32 слова сегмента, эта область называется Segment Access Area;

- стандартный (Standard) – программный доступ возможен ко всему диапазону адресов сегмента.

- защищенный сегмент и основной сегмент имеют ограниченный доступ к загрузочному сегменту.

- основной сегмент имеет ограниченный доступ к защищенному сегменту.

- память данных разбита на три сегмента с конфигурируемым объемом. Спецификацией определены права доступа к каждому сегменту ОЗУ из соответствующего сегмента программной памяти.

Гибкая система защиты интеллектуальной собственности CodeGuard™ позволяет не только разрабатывать устройства, защищенные от кражи ПО, но и разрешать сторонним производителям использование прошитых программных модулей, обеспечив соответствующие права доступа.

Периферийные модули

Все периферийные модули 16-битных семейств Microchip значительно переработаны по сравнению с аналогичными в 8-битных семействах. Единственный модуль, который полностью перенесен из предыдущей архитектуры – это модуль CAN в микроконтроллерах dsPIC30 (полный аналог модуля CAN семейства PIC18F458).

Порты ввода-вывода

Все порты ввода-вывода общего назначения семейства dsPIC30 имеют три управляющих регистра: TRISx – направление порта (комплементарный драйвер – выход, третье состояние - вход), PORTx – чтение регистра возвращает логический уровень непосредственно на выходе, запись осуществляется в регистр-защелку порта, LATx – чтение возвращает значение регистра-защелки порта, запись так же осуществляется в регистр защелку.

Часть выводов контроллера (в dsPIC30 до 24 выводов в 80-выводном корпусе) имеют функцию генерирования прерывания по изменению состояния. Вектор прерывания для этого события один.

Все порты ввода-вывода имеют на входе триггер Шмитта, и защитные диоды на линии питания и земли.

Структура портов ввода-вывода семейств dsPIC33 и PIC24F/H аналогична dsPIC30. Все цифровые выводы толерантны к +5 В. Каждый вывод может быть индивидуально сконфигурирован как выход с открытым стоком.

Контроллеры семейств dsPIC33 и PIC24F/H полностью совместимы по выводам и частично совместимы с семейством dsPIC30 (за исключением одного вывода). Контроллеры PIC24F/dsPIC30 допускают величину втекающего/вытекающего тока портов до 25 мА, семейства PIC24H/dsPIC33 – до 4 мА.

Таймеры

Микроконтроллеры dsPIC30/PIC24F имеют в своем составе пять 16-битных таймеров, четыре из которых могут объединяться в два 32-битных. Основные особенности таймеров:

- все таймеры имеют регистр периода при совпадении с которым таймер сбрасывается, устанавливается флаг и, если разрешено, генерируется прерывание.

- все таймеры имеют предделитель с коэффициентами 1/1, 1/8, 1/64 и 1/256.

- один из таймеров может тактироваться от встроенного низкочастотного (32 кГц) кварцевого генератора и работать в асинхронном счетном режиме.

- четыре таймера могут работать в счетном режиме и режиме разрешения счета (таймер инкрементируется только тогда, когда на выводе таймера присутствует разрешающий логический уровень).

- два таймера могут генерировать строб запуска АЦП.

Семейства dsPIC33/PIC24H имеют полностью аналогичные таймеры, их количество увеличено до 9 (восемь из них могут объединяться в четыре 32-битных таймера).

Модули захвата

В отличие от 8-битных семейств, в которых модули захвата/сравнения/ШИМ физически представляют собой один модуль CCP, режим работы которого выбирается программно, модули захвата, сравнения и генерации ШИМ в 16-битных семействах физически независимы. Модули захвата всех 16-битных семейств идентичны.

Модуль захвата, как правило, применяется для вычисления длительности внешних процессов, например периода входного сигнала, длительности одиночного импульса и т. п. При возникновении ожидаемого внешнего события (передний фронт, задний фронт) в 16-битный регистр модуля захвата заносится значение связанного с ним таймера, если разрешено – генерируется прерывание.

Модули захвата контроллеров dsPIC30/33 и PIC24F/H имеют следующие особенности:

- захват значения таймера при каждом событии, при каждом 4 событии, при каждом 16 событии, захват значения таймера при каждом фронте.

- 4-х уровневый FIFO буфер. Прерывание может генерироваться модулем захвата при заполнении буфера на выбираемую пользователем величину уровней. Доступен флаг, сигнализирующий о переполнении FIFO.

Контроллеры dsPIC30 имеют от 1 до 8 модулей захвата, PIC24F - 5 модулей захвата, PIC24H/dsPIC33 - 8 модулей захвата.

Модули сравнения

Модуль сравнения используется для генерации на выводе контроллера определенной последовательности логических уровней. При совпадении значения связанного таймера с 16-битным регистром модуля на выводе формируется заданный логический уровень или инвертируется предыдущий. Если разрешено, генерируется прерывание.

Модули сравнения семейств PIC24F/H и dsPIC30/33 имеют следующие особенности:

- два регистра сравнения позволяют генерировать два фронта на выходе при одном инкременте таймера. Возможна генерация центральносмещенного ШИМ сигнала.

- функция аппаратного отключения позволяет прекращать генерацию сигнала на выходе при аппаратной неисправности (например, перегрузке мощных ключей).

- возможность генерации набора ШИМ сигналов для управления двигателями и источниками питания. Поддерживается управление полумостовой и мостовой схемой с учетом паузы для исключения сквозных токов через мощные ключи.

Если модули сравнения используются для генерации ШИМ сигнала, разрядность ШИМ зависит от частоты. Так, при максимальной производительности 40 MIPS и частоте генерации 39 кГц разрядность ШИМ будет равна 10. Минимальная частота генерации 2,38 Гц (при производительности 40 MIPS).

Контроллеры dsPIC30 имеют от 1 до 8 модулей сравнения, PIC24F - 5 модулей сравнения, PIC24H/dsPIC33 - 8 модулей сравнения.

Модули генерации ШИМ сигнала для специальных приложений

ШИМ сигнал используется во многих специальных приложениях: управление двигателями постоянного и переменного тока, управление осветительными приборами, источники питания, и др. Большинство этих задач требуют реализации дополнительных функций, таких как обеспечение аппаратного отключения генератора ШИМ, реализации паузы между переключением силовых ключей, генерации симметричного сигнала на раздельных выводах.

Некоторые 16-битные микроконтроллеры Microchip имеют в своем составе модули генерации ШИМ сигнала, функциональность которых значительно расширена по сравнению со стандартным модулем сравнения.

Модуль управления двигателями и источниками питания

Модуль управления двигателями присутствует только в контроллерах с DSP-ядром – dsPIC30/33. Для реализации управления двигателями и источниками питания в PIC24F/H могут использоваться модули сравнения.

Основные особенности модуля управления двигателями и источниками питания:

- от 6 до 8 каналов, комплементарный или независимый режим работы пары каналов.

- аппаратная генерация задержки переключения мощных ключевых элементов (в контроллерах с 6 каналами – один генератор задержки, в контроллерах с 8 каналами – два генератора задержки).

- программная конфигурация активного уровня на каждом выходе модуля.

- генерация центральносмещенного ШИМ сигнала.

- возможность установки на каждом выводе фиксированного логического уровня.

- один или два входа аппаратного аварийного отключения модуля.

- настраиваемая генерация строба запуска АЦП.

Модуль может использоваться для управления асинхронными двигателями, двигателями постоянного тока, безколлекторными двигателями постоянного тока, для построения эффективных источников питания.

Модуль генерации ШИМ для источников питания

В июле 2006 года компания Microchip анонсировала три новых микроконтроллера семейства dsPIC30: dsPIC30F1010, dsPIC30F2020 и dsPIC30F2023. Эти микроконтроллеры содержат два уникальных модуля – модуль генерации ШИМ для управления источниками питания (PSPWM - Power Supply PWM) и модуль универсального компаратора (SMPSC - Switch Mode Power Supply Comparator).

Эти контроллеры позиционируются для разработки корректоров коэффициента мощности, импульсных (в том числе регулируемых) источников питания, построенных по всем возможным схемам.

Структура модуля PSPWM похожа на структуру модуля управления двигателями. Отличие состоит в большей гибкости настроек и измененном методе тактирования. В системах электропитания модуль PSPWM может работать совместно с модулем SMPSC, который в данном случае предназначен для организации обратной связи.

Основные характеристики «связки» PSPWM + SMPSC:

- четыре генератора ШИМ. Каждый имеет два выхода (всего восемь), которые могут работать в противофазе. Каждый генератор имеет независимую временнУю базу, что позволяет реализовать следующие режимы работы:

- стандартный ШИМ

- комплементарный ШИМ

- противофазный ШИМ

- многофазная система ШИМ сигналов

- ШИМ с регулируемой фазой

- все четыре ШИМ генератора позволяют изменять в реальном времени частоту сигнала, коэффициент заполнения, сдвиг фазы.

- поддержка паузы переключения для защиты мощных ключей от сквозного тока.

- генераторы обладают уникальной разрешающей способностью по времени: (при 30 MIPS) разрешающая способность коэффициента заполнения – 1.1 нсек, разрешающяя способность схемы задержки на переключение – 4.2 нсек, разрешающая способность сдвига фазы – 4.2 нсек, разрешающая способность установки периода ШИМ – 8.4 нсек. Такие параметры позволяют на выходе модуля получить ШИМ сигнал с частотой 937 кГц и диапазоном регулировки скважности 10 бит.

- независимые входы аварий – общий и перегрузки по току.

- каждый ШИМ генератор имеет схему сравнения для запуска АЦП.

- универсальный компаратор имеет 16 входов, 10-битный ЦАП для установки опорного напряжения.

- в качестве опорного ЦАП может использовать внешнее напряжение, 50% напряжения питания, внутренний стабильный (1%) источник опорного напряжения 1.2 В.

- компаратор может запускать любой из 4 ШИМ генераторов, вызывать прерывание. Схема строба прерываний подключена к компаратору через настраиваемый НЧ фильтр.

На сегодняшний день модули PSPWM и SMPSC доступны только в трех указанных контроллерах семейства dsPIC30.

Модуль интерфейса квадратурного энкодера

Системы управления двигателями, как правило, подразумевают наличие обратной связи по положению, которая может быть реализована с помощью датчиков Холла, оптических датчиков, квадратурного энкодера. В последнем случае совместно с модулем управления двигателями может использоваться аппаратный модуль интерфейса квадратурного энкодера. Модуль присутствует только в контроллерах dsPIC30/33.

Основные особенности модуля:

- 16-битный счетчик импульсов (с возможностью инкремента и декремента) и флаг направления вращения.

- предделитель счетчика импульсов, регистр периода (при равенстве регистру периода счетчик сбрасывается, и, если разрешено, генерируется прерывание).

- возможность использование модуля в качестве таймера-счетчика общего назначения.

- три входа – два для квадратурно смещенных импульсов и один индексный, который может использоваться для сброса счетчика.

- программируемый цифровой фильтр на каждом входе – позволяет использовать даже дешевые механические энкодеры с большим временем дребезга контактов.

Компараторы

Два аналоговых компаратора присутствуют только в микроконтроллерах PIC24F. Основные особенности компараторов:

- все выводы компараторов могут быть скоммутированы на порты микроконтроллера. Доступны программные флаги логических уровней на выходах компараторов.

- гибкая настройка подключения выводов компараторов.

- аппаратная инверсия выходного сигнала компаратора.

- наличие конфигурируемого источника опорного напряжения.

- физические параметры компараторов соответствуют параметрам аналогичных модулей в 8-битных микроконтроллерах Microchip.

Модули АЦП

Модули АЦП 16-битных семейств Microchip можно разделить на четыре вида, каждый из которых обладает специфическими функциями.

10-битный АЦП dsPIC30

АЦП последовательного приближения - осуществляет оцифровку сигнала со скоростью до 500 тыс. выборок в секунду. АЦП имеет 4 схемы выборки-хранения с дифференциальным входом (что позволяет проводить одновременную выборку по 4 дифференциальным каналам), от 6 до 16 каналов, гибкий мультиплексор каналов.

Интересной особенностью этого модуля является наличие программируемого сэмплера, позволяющего производить выборку, а затем квантование по заданному алгоритму переключения каналов.

АЦП имеет 16-уровневый буфер и схему форматирования результата – результат может быть представлен в виде знакового, беззнакового, целого, числа с фиксированной точкой. Схема форматирования осуществляет заданное выравнивание результата внутри 16-битного слова буфера. Использование сэмплера позволяет размещать результаты преобразования в буфере по заданной схеме и генерировать прерывание после произвольного числа преобразований от 1 до 16-и.

В качестве опорного напряжения для квантования используются либо шины питания, либо внешние опорные напряжения Vref- и Vref+. Типовые значения интегральной и дифференциальной нелинейности АЦП составляют +/- 0,5 МРЗ.

12-битный АЦП dsPIC30

АЦП последовательного приближения - осуществляет оцифровку сигнала со скоростью 100 тыс. выборок в секунду. АЦП имеет одну схему выборки хранения с дифференциальным входом и от 8 до 16 каналов.

Так же как и в 10-битном АЦП присутствует сэмплер преобразования, 16-уровневый буфер, схема формирования результата. Преобразование может запускаться программно, от строба модуля управления двигателями, при переполнении таймера, от внешнего прерывания.

Типовые значения интегральной и дифференциальной погрешности не превышают +/- 1 МРЗ.

10-битный АЦП PIC24F

Является аналогом 10-битного АЦП dsPIC30, но содержит одну дифференциальную схему выборки-хранения. Схема мультиплексирования позволяет подать на прямой и инверсный входы схемы ВР сигнал любого аналогового канала. Точностные характеристики соответствуют 10-битному АЦП dsPIC30. Все микроконтроллеры семейства PIC24F имеют один модуль АЦП (16 каналов).

АЦП PIC24H/dsPIC33 c конфигурируемой разрядностью

Основной особенностью этого модуля АЦП является возможность программной конфигурации количества уровней квантования. Один бит в управляющем регистре позволяет настроить модуль как 10-битный АЦП с 4 дифференциальными схемами ВХ, либо как 12-битный АЦП с 1 дифференциальной схемой ВХ.

Значительно увеличена скорость преобразования – для 10-биного режима она составляет 1,1 млн. выборок в секунду, для 12-битного – 500 тыс. выборок в секунду. Контроллеры PIC24H/dsPIC33 могут иметь в своем составе до двух модулей АЦП (до 32-х каналов) что предоставляет уникальную возможность - удвоить скорость преобразования, используя оба модуля параллельно.

В остальном функциональность модуля аналогична 10- или 12-битному АЦП dsPIC30 в зависимости от выбранного режима работы (разрядности).

Модуль АЦП PIC24H/dsPIC33 имеет возможность генерирования адреса для контроллера DMA, что позволяет размещать результаты преобразований по разным каналам в разных секторах буфера DMA.

Коммуникационные интерфейсы

UART

Модули UART 16-битных семейств PIC24F/H и dsPIC30/33 существенно переработаны по сравнению с аналогичными интерфейсами в 8-битных семействах. Основные особенности модулей UART:

- полнодуплексный 8- и 9-битный обмен, альтернативные выводы.

- возможность передачи и приема бита четности при 8-битном обмене.

- один или два стоповых бита.

- собственный генератор с 16-битным предделителем (для dsPIC30 при 30 MIPS – от 29 бод до 1,875 Мбод, для PIC24F при 16 MIPS – от 15 бод до 1 Мбод, для PIC24H/dsPIC33 при 40 MIPS – от 38 бод до 2,5 МБод).

- 4-уровеневый буфер FIFO приемника и 4-уровневый буфер FIFO передатчика.

- детектирование ошибок четности, переполнения буфера и ошибки формата кадра.

- поддержка 9-битного обмена с функцией детектирования адреса.

- диагностический режим «эхо» (loopback).

- аппаратная поддержка автоподстройки скорости обмена (для dsPIC30 возможно перенаправление входа RX на вход модуля захвата, для PIC24F/H и dsPIC33 автоподстройка осуществляется логикой самого модуля).

- поддержка LIN 2.0 спецификации: генерирование поля Synk, поля Break (для dsPIC30 – только программно, для PIC24F/H, dsPIC33 – полная аппаратная поддержка), вывод контроллера из энергосберегающего режима по фронту на входе RX.

- раздельные векторы прерываний для всех ошибок модуля UART (только для PIC24F/H, dsPIC33).

- возможность аппаратного управления потоком – сигналы CTS и RTS (только для PIC24F/H, dsPIC33).

- поддержка физического уровня спецификации IrDA® (только для PIC24F/H, dsPIC33).

Контроллеры dsPIC30 имеют от 1 до 2-х модулей UART, все контроллеры семейств PIC24F/H и dsPIC33 имеют два модуля UART. Следует заметить, что в отличие от аналогичного модуля 8-битных семейств, модуль UART 16-разрядных контроллеров не поддерживает режим синхронного обмена. Для реализации этой функции рекомендуется использовать модуль SPI.

SPI™

В 8-битных семействах Microchip модуль SPI был объединен с интерфейсом I2C в модуль MSSP, который мог работать только в одном, выбранном программно режиме. Это накладывало некоторые ограничения на функциональность системы. В 16-битных семействах модули SPI и I2C являются физически независимыми и могут функционировать параллельно. Все 16-битные семейства имеют модули SPI со следующими характеристиками:

- 8- и 16-битный режимы обмена.

- режимы работы «ведомый» и «ведущий».

- выбор активного уровня на линии тактирования. Выбор уровня на линии тактирования в режиме ожидания.

- 8-уровневый буфер FIFO (только для PIC24F).

- генератор линии тактирования с двумя предделителями (максимальная частота 10 МГц)

- фреймовый режим обмена – позволяет подключать к модулю современные АЦП и голосовые кодеки.

Микроконтроллеры dsPIC30 имеют от 1 до 2-х модулей SPI, семейства PIC24F/H, dsPIC33 – два модуля SPI.

I2C™

Все 16-битные семейства имеют модули I2C со следующими характеристиками:

- полная поддержка следующих режимов: «ведомый», «ведущий с одним мастером на шине», «ведущий с несколькими мастерами на шине, с возможностью детектирования коллизий и арбитражем»

- поддержка 8- и 10-битной адресации.

- поддержка сообщения общего вызова спецификации I2C. Поддержка зарезервированных протоколом адресов.

- работа в режиме повторителя – прием всех сообщений вне зависимости от значения поля адреса.

- опция удержания тактового сигнала, управление длительностью фронта.

- уровни спецификаций I2C и SMBus.

- прерывание при совпадении принятого адреса с заданной 10-битный маской (может использоваться для вывода контроллера из режима пониженного потребления IDLE).

- генератор тактирования (шина SCL).

- поддержка спецификаций 100 кГц, 400 кГц и 1 МГц.

Модуль I2C 16-битных семейств имеет расширенный набор флагов, позволяющий сократить размер и время выполнения кода обработчика прерывания по сравнению с 8-битными семействами.

Микроконтроллеры dsPIC30 имеют 1 модуль I2C, PIC24F – 2 модуля I2C, dsPIC33/PIC24H – от 1 до 2-х модулей I2C.

DCI

Высокая производительность и наличие DSP-ядра позволяют использовать микроконтроллеры dsPIC30/33 в задачах цифровой обработки звуковых сигналов, в частности, для реализации голосовых вокодеров и систем распознавания речи.

Модуль DCI предназначен для обмена данными с микросхемами голосовых кодеков, поддерживаются следующие режимы работы:

- последовательный интерфейс с фреймовой синхронизацией – используется большинством современных кодеков. Позволяет в одном фрейме передавать как звуковые данные по нескольким каналам, так и управляющую информацию.

- I2S (Inter-IC Sound) интерфейс – устаревший интрефейс, однако до сих пор используемый в высококачественных звуковых кодеках (Wolfson, AKM, и т. д.).

- Режим совместимый со спецификацией AC’97.

Модуль DCI имеет собственный генератор частоты обмена, два 4-уровневых буфера приемника и передатчика, поддерживает до 16 временнЫх слотов, 8-16 битную разрядность звуковых данных.

Модуль DCI присутствует только в контроллерах с DSP-ядром (dsPIC30/33).

CAN

Модуль CAN контроллера dsPIC30 полностью идентичен аналогичному модулю 8-битного семейства PIC18F458 (спецификация CAN 2.0A/B). Модуль E(nchanced)CAN PIC24H/dsPIC33 значительно расширен по сравнению с CAN dsPIC30. Основные особенности CAN/ECAN модулей семейств dsPIC30/33 и PIC24H:

- поддержка спецификаций CAN 1.2, CAN 2.0A и CAN2.0B.

- прием и передача фреймов данных стандартного и расширенного формата.

- длина фрейма данных – 0-8 байт.

- программируемая скорость обмена до 1 Мбод.

- два буфера приемника с выбираемым приоритетм (CAN), до 32 8-байтных буферов приемника с выбираемым приоритетом (ECAN).

- 6 фильтров сообщений (CAN), 16 фильтров сообщений (ECAN).

- 2 маски фильтров сообщений (CAN), 3 маски фильтров сообщений (ECAN).

- поддержка адресации DeviceNet™ (ECAN).

- три буфера передатчика с выбираемым приоритетом (CAN), 8 8-байтных буферов передатчика с выбираемым приоритетом (ECAN).

- программируемая функция вывода из энергосберегающего режима.

- перенаправление событий приемника на вход модуля захвата (только ECAN – ведение логов, сетевая синхронизация).

Контроллеры dsPIC30 имеют от 1 до 2-х CAN модулей, PIC24H/dsPIC33 - от 1 до 2-х ECAN модулей.

Параллельный порт

Параллельный адресуемый мастер-порт (PMP) присутствует только в контроллерах семейства PIC24F. Он позволяет организовать обмен данными с различными устройствами – ЖКИ индикаторами, внешними микросхемами FLASH и SRAM памяти, картами памяти CompactFlash®, жесткими дисками и т. п.

Параллельный мастер-порт имеет следующие характеристики:

- две линии выбора кристалла (CS), управляющие линии (ByteEn, RD, WR, индивидуальные или совмещенные стробы записи/чтения). Активный логический уровень всех управляющих сигналов может быть настроен программно.

- 16-битная конфигурируемая шина адреса (любая линия может быть включена или отключена). Возможность автоматического инкремента или декремента адреса.

- 8-битная или 16-битная (только для контроллеров в 100-выводных корпусах) шина данных.

- возможность работы в мультиплексном режиме шины данных и шины адреса.

- программируемые временнЫе параметры.

- 4-х уровневый буфер данных.

- выбор пороговых уровней (TTL, триггер Шмитта).

- поддержка режима «ведомый» - функциональность, аналогичная модулю PSP в 8-битных семействах.

Параллельный порт доступен только в семействе PIC24F. В микроконтроллерах с количеством выводов 64 и 80 PMP имеет 8-битную шину данных, в микроконтроллерах с количеством выводов 100 - 16-битную шину данных.

Модуль CRC

Модуль CRC (cyclic redundancy check) предназначен для аппаратного вычисления циклической избыточной суммы, которая используется в коммуникационных протоколах для проверки целостности пакета.

Модуль может использоваться для вычисления циклического кода с произвольным полиномом длиной от 1 до 16 бит. Модуль имеет буфер данных объемом 8 слов при длине полинома от 7 до 16 бит и объемом 16 слов при длине полинома менее 7 бит. По завершению вычисления может генерироваться прерывание.

Модуль вычисления CRC доступен только в семействе PIC24F.

Модуль часов реального времени и календаря (RTCC)

Модуль доступен только в контроллерах PIC24F. Модуль тактируется от внутреннего низкочастотного (32 кГц) кварцевого генератора (необходимо использование внешнего резонатора) и осуществляет аппаратный подсчет времени, смену календарных дней. RTTC имеет следующие характеристики:

- подсчет секунд, минут и часов, 24-часовой формат.

- календарь: день недели, дата, месяц, год. Диапазон: 2000 – 2009 год, учет високосных годов.

- BCD формат представления данных.

- программная и аппаратная калибровка: +/- 2,64 секунды в месяц.

- гибкая система тревог, выход импульса тревоги.

Модуль RTCC не поддерживает автоматическую смену летнее/зимнее время – эту функцию необходимо реализовывать программно.

JTAG интерфейс

JTAG интерфейс предназначен для граничного сканирования (проверки целостности системы) и внутрисхемного программирования и отладки микроконтроллеров. Впервые JTAG интерфейс стал доступен в новых 16-битных семействах PIC24F/H и dsPIC33. На сайте компании опубликованы ВSDL-файлы для всех микроконтроллеров с JTAG интерфейсом [3], а спецификация программирования Flash памяти будет доступна в ближайшее время.

Программные и аппаратные средства разработки

Среды разработки

Основной средой разработки для всех семейств (и 8- и 16-битных) является MPLAB IDE, которую предоставляет компания Microchip. Среда разработки бесплатная, актуальная версия на сентябрь 2006 года – 7.421).

Среда разработки MPLAB имеет следующие встроенные средства и возможности:

- менеджер проекта и рабочей области

- текстовый редактор с подсветкой кода для ассемблеров всех семейств и языка Си. Возможен парсинг кода и вывод списка элементов программы (функций, переменных, констант, структур, и т. п.). Текстовый редактор поддерживает запись и выполнение макросов.

- ассемблер для всех семейств Microchip. Для 16-битных контроллеров - ассемблер ASM30. В состав среды входят заголовочные файлы и скрипты линкера для всех контроллеров.

- программный симулятор для всех семейств Microchip, который обеспечивает симуляцию большинства периферийных модулей, трассировку выполняемого кода, произвольное число точек останова, пошаговое выполнение. Симулятор имеет счетчик времени выполнения, логический анализатор (графическое представление изменений логических уровней на выводах контроллера).

Симулятор позволяет имитировать работу внешних устройств: аналоговый сигнал на входе АЦП, RS-232 терминал, и т. п. Возможно изменение любого служебного регистра или ячейки ОЗУ в соответствии с заданной в текстовом файле последовательностью.

Начиная с версии 7.40 в состав симулятора входит модуль DMCI (Data Monitor and Control Interface). Модуль устанавливается в виде отдельного плагина и позволяет отображать в реальном времени данные массива в виде графика и изменять значение по любому адресу в ОЗУ.

Наличие окон Watch (значения переменных) и Local (то же самое, но для локальных и автоматических переменных функции) характерно как для симулятора, так и для интерфейса внутрисхемных отладчиков и эмуляторов.

Среда разработки поддерживает использование плагинов как от Microchip, так и от сторонних разработчиков. Например, плагин Visual Initializer от Microchip позволяет с помощью визуальных средств настроить все периферийные модули контроллера и получить на выходе код инициализации на языке Си или ассемблере.

Кроме собственных компиляторов MCC18 и MCC30, MPLAB IDE поддерживает множество компиляторов с языков высокого уровня сторонних производителей (Hi-Tech, IAR, CCS).

Среда разработки MPLAB IDE позволяет использовать все программаторы Microchip: PICSTART+, Promate II, Promate III, программатор начального уровня PICkit 2. Основным инструментом отладки является внутрисхемный отладчик-программатор MPLAB ICD2, совместимый с любым контроллером 16-битного семейства.

Более дорогими инструментами отладки являются внутрисхемные эмуляторы ICE 2000 и ICE 4000. Последний предназначен для эмуляции 16-битных семейств.

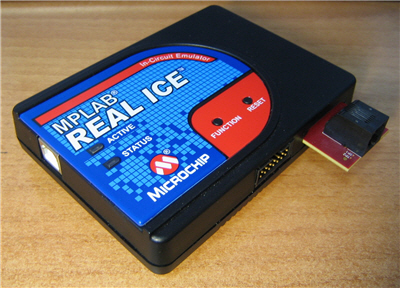

Летом 2006 года компания Microchip анонсировала выпуск нового внутрисхемного отладчика-эмулятора REAL ICE. На сентябрь 2006 года этот эмулятор находится на стадии производственного тестирования. Начало серийного производства запланировано на октябрь-ноябрь 2006 года.

Полезным для разработчика будет интегрированная система документации на среду разработки, симулятор, ассемблеры и поддержка систем контроля версий: CVS, Subversion, Merant PCVS, MS SourceSafe.

В составе среды разработки MPLAB IDE поставляется ASM30 - ассемблер для 16-битных семейств. Так как все контроллеры dsPIC30/33 и PIC24F/H совместимы по системе команд (за исключением инструкций ядра ЦОС), возможно использование разработанного ранее кода при переходе на другое 16-битное семейство.

Кроме MPLAB IDE можно упомянуть среду разработки от известного производителя компиляторов для встраиваемых систем IAR IDE for dsPIC. На сентябрь 2006 года актуальной является версия 1.20B, которая поставляется в комплекте с компилятором языка Си. Продукты IAR Systems являются достаточно популярными в России для контроллеров семейств x51, ARM, AVR, однако для профессиональной разработки приложений для dsPIC30/dsPIC33/PIC24F/PIC24H среда IAR малопригодна – отсутствует поддержка программаторов и отладчиков, не поддерживается симуляция периферии, симуляция ядра выполнена со значительными ошибками.

В сентябре 2006 года компания HI-TECH Software, известная российским разработчикам одним из лучших компиляторов с языка Си для 8-битных микроконтроллеров Microchip, анонсировала выход новой версии среды разработки HI-TIDE 3.11, в которую добавлена поддержка 16-битных семейств на уровне создания проекта. К сожалению, HI-TIDE не поддерживает симуляцию для 16-битных контроллеров и аппаратные средства разработки Microchip, поэтому пока она не пригодна для профессионального использования.

Для пользователей операционной системы Linux можно рекомендовать среду разработки с открытым исходным кодом Piklab. Из 16-битных семейств она пока поддерживает только dsPIC30, но проект активно развивается – можно ожидать добавления PIC24F/H и dsPIC33 в будущем.

Компиляторы с языка Си

Для 16-битных семейств компания Microchip предлагает компилятор MPLAB C30 (актуальная версия на сентябрь 2006 года – 2.03), в состав которого входят: собственно компилятор исходных файлов в объектные; линкер; генератор библиотечных файлов. Компилятор C30 основан на известном компиляторе с открытым исходным кодом GCC, однако выполняемые файлы доступны только для ОС Windows. На сайте компании Microchip размещены исходные коды компилятора для последней выпущенной версии, что позволяет произвести сборку самостоятельно под любую операционную систему.

Основные особенности компилятора C30:

- ANSI C совместимый, в комплекте поставляются стандартные библиотеки.

- поддержка типов 32-bit double и 64-bit double, 64-битного целого (long long).

- поддержка всех 16-битных семейств Microchip.

- поддержка смешанного кода Си + asm.

- поддержка расширенных настроек оптимизации кода.

- наличие встроенных (intrinsincs) функций для работы с DSP-ядром.

Microchip предоставляет два варианта компилятора – платная версия и полнофункциональная «студенческая» версия. Студенческая версия работает без ограничений 60 дней, далее возможна только компиляция без использования оптимизации.

Кроме MPLAB C30 можно отметить следующие компиляторы с языка Си (актуальность - сентябрь 2006 года):

HI-TECH dsPICC v. 9.60 – компилятор от известного австралийского производителя HI-TECH Software, который известен российским разработчикам одним из лучших компиляторов для 8-битных контроллеров Microchip. Компилятор интегрируется в среду разработки MPLAB IDE, но может работать и в составе среды HI-TIDE 3.11 от HI-TECH (см. пункт «Среды разработки»). Доступны версии компилятора как для OS Windows, так и для Linux.

IAR IDE for dsPIC 1.20B – поставляется в составе интегрированной среды известного производителя средств разработки для встраиваемых систем IAR Systems [9]. Малопригоден для профессионального применения. Последняя версия компилятора доступна уже больше года, обновлений пока не предвидится. Компилятор поддерживает только небольшое число контроллеров семейства dsPIC30.

microC for dsPIC 2.0.0.0 – компилятор и среда разработки от компании mikroElektronika [10]. Малопригоден для профессионального применения, так как не имеет возможности запуска из командный строки и лишь частично удовлетворяет спецификации ANSI C. Компания microElectornica так же предлагает компиляторы языков Pascal и Basic для 16-битных семейств Microchip, однако они имеют те же ограничения для профессионального применения.

В качестве примера приведем результаты сравнительного теста компиляторов C30, dsPICC и IAR. Компилировался один из вариантов теста Whetstone (вычисления с плавающей точкой). Симуляция проводилась в среде разработки MPLAB IDE для компиляторов dsPICC и C30 и в среде IAR для компилятора IAR 1.20B. Результаты симуляции проверены на макете с контроллером dsPIC30F6012 (~29.25 MIPS, тактовая частота – 117.9648 МГц):

| Производитель | Компилятор | размер double, бит | модель памяти | уровень оптимизации | кол-во командных тактов (симуляция), млн | кол-во командных тактов (макет), млн | время выполнения, сек | Объем кода, кБайт | Субъективная оценка (максимум 5 баллов) |

|---|---|---|---|---|---|---|---|---|---|

| IAR Systems | IAR 1.20B | 32 | small | по размеру | 26.2 | 27.4 | 0.91 | 6.0 | 3 |

| Microchip | C30 2.03 | 32 | small | по размеру | 28.8 | 28.8 | 0.96 | 4.5 | 5 |

| Hi-Tech Software | HT dsPICC 9.50 | 32 | small | максимальная | 61.7 | 61.6 | 2.05 | 7.1 | 2 |

| IAR Systems | IAR 1.20B | 64 | small | по размеру | 43.5 | 47.3 | 1.58 | 9.7 | 3 |

| Microchip | C30 2.03 | 64 | small | по размеру | 48.1 | 48.0 | 1.60 | 7.5 | 2 |

Из таблицы видно, что компилятор HI-TECH значительно уступает IAR и C30 как по плотности кода, так и по времени выполнения. Для тестирования использовалась одна из первых версий, однако проверка последней версии от 19 сентября 2006 года показала, что хотя время выполнения теста уменьшилось примерно на 10 процентов, плотность кода осталась прежней.

Компилятор IAR немного опережает C30 по скорости выполнения, однако заметно проигрывает по плотности кода. Из таблицы видно, что в симуляторе среды IAR допущены значительные нарушения – количество командных тактов указанных симулятором отличается от реального.

Библиотеки

Компания Microchip предоставляет разработчикам большое количество библиотек для компилятора MPLAB C30, что является еще одним аргументов для использования его в качестве основного средства разработки. Часть библиотек распространяется бесплатно, некоторые библиотеки – платные, однако с ними можно ознакомиться, скачав демонстрационную версию с сайта компании после регистрации. Платные библиотеки доступны для скачивания в виде скомпилированных библиотечных файлов, что ограничивает область их применения. Возможны различные формы оплаты при приобретении библиотек – либо единовременная оплата, либо лицензионные отчисления. В таблице приведен список библиотек, предоставляемых компанией Microchip для 16-битных семейств:

| Библиотека | Бесплатная 2) | Реализация | Поддерживаемые семейства |

|---|---|---|---|

| Математические функции | + | asm | PIC24F/H, dsPIC30/33 |

| Управление периферийными модулями | + | Си | dsPIC30, PIC24F/H, dsPIC33 |

| Функции ЦОС | + | asm | dsPIC30/33 |

| Софт-модем | - 3) | Си | dsPIC30/33 |

| Распознавание речи | - | Си + asm | dsPIC30/33 |

| Шумоподавление | - | Си | dsPIC30/33 |

| Подавление акустического эха | - | Си + asm | dsPIC30/33 |

| Подавление эха в каналах связи | - | Си | dsPIC30/33 |

| Симметричные алгоритмы шифрования | - 4) | Си | PIC24F/H, dsPIC30/33 |

| Несимметричные алгоритмы шифрования | - | Си | PIC24F/H, dsPIC30/33 |

| Сжатие речи | - 5) | Си | dsPIC30/33, PIC24F/H |

| Стек протоколов TCP/IP | + | Си | PIC24F/H, dsPIC30/33 |

| FAT16 | + | Си | PIC24F/H, dsPIC30/33 |

Библиотека математических функций

Исходные коды доступны на сайте Microchip и в составе компилятора MPLAB C30. Для увеличения скорости выполнения библиотеки реализованы на ассемблере, но все функции могут быть вызваны из Си-кода. Тип аргументов и возвращаемых результатов – IEEE-754 (плавающая точка), реализованы арифметические, тригонометрические, логарифмические функции, функция взятия корня, функции округления и т. д., т.е. все стандартные математические функции языка Си.

Библиотека работы с периферийными модулями

Исходные коды доступны на сайте Microchip и в составе компилятора MPLAB C30. Реализованы функции для работы со следующими периферийными модулями: порты ввода-вывода и внешние прерывания, таймеры, модули захвата и сравнения, модуль ШИМ для управления двигателями, модуль квадратурного энкодера, RTCC, CRC, UART, SPI, I2C, DCI, CAN, 10- и 12-битный АЦП.

Библиотека функций ЦОС

Исходные коды доступны на сайте Microchip и в составе компилятора MPLAB C30. Библиотека реализована на ассемблере, функции могут быть вызваны из кода на языке Си. Библиотека содержит 49 функций, которые можно разделить на следующие группы:

- векторные операции: сложение и вычитание векторов, свертка, вычисление корреляционной функции, максимум, минимум, умножение и масштабирование

- операции с матрицами: сложение, вычитание, умножение, масштабирование, транспонирование

- оконные функции: функции окон Блекмана, Хамминга, Ханнинга, Кайзера и Батлета

- функции фильтрации: КИХ фильтрация, БИХ фильтрация

- функции преобразований: дискретное косинусное преобразование, БПФ, обратное БПФ

Все функции библиотеки оптимизированы по скорости – преобразование Фурье (256 отсчетов) выполняется за 476 мкс (40 MIPS).

Библиотека софт-модема

Предназначена для реализации программных модемов по спецификациям ITU-T V.21, V.22, V22bis, V.23, V.32 и V.32bis.

Пакет, включающий реализацию V.22bis/V.22 , V.23, V.21 поставляется бесплатно. Поддержка остальных спецификаций осуществляется на платной основе. Для реализации V.32bis (скорость обмена от 4,8 кбод до 14,4 кбод, QAM/TCM модуляция) необходима производительность не менее 15 MIPS.

Библиотека распознавания речи

Предназначена для реализации систем дистанционного управления речью. Так как в библиотеке реализовано распознавание английской речи, библиотека вряд ли будет интересна Российским разработчикам.

Библиотека шумоподавления

Библиотека предназначена для увеличения соотношения сигнал/шум речевого сигнала в следующих приложениях: системы «hands-free», системы оповещения, телекоммуникации, телефонные гарнитуры и т. д. Библиотека поставляется на платной основе. Применение библиотеки позволяет улучшить SNR на 10-20 дБ для типовых приложений, для использования необходима производительность 1 MIPS.

Библиотека подавления акустического эха

Предназначена для подавления эха и акустического самовозбуждения в системах громкой связи, системах оповещения, беспроводных телефонных аппаратах (обратная акустическая связь по корпусу трубки), и т. п. В библиотеке применяется адаптивный цифровой фильтр с детектором активности речи, полностью реализованный на ассемблере с целью увеличения скорости выполнения и уменьшения объема используемой программной памяти. Алгоритм обеспечивает подавление эха как минимум на 40 дБ (типовое значение 50 дБ). Библиотека может использоваться совместно с библиотекой шумоподавления.

Библиотека подавления эха в каналах связи

Предназначена для использования в коммуникационных системах, для подавления отражения аналоговых сигналов в линиях связи. Полностью соответствует стандарту ITU-T G.168. Типовое значения коэффициента подавления 70 дБ (минимальное 40 дБ).

Библиотека симметричных алгоритмов шифрования

Предоставляются следующие функции:

- хэш-алгоритмы SHA-1 (поток до 423 кБайт/с), MD5 (поток до 656 кБайт/с).

- алгоритмы шифрования: AES-128, T-DES. При последовательности шифрование-дешифрование обеспечивается следующая скорость потока данных: для AES-128 – 232 кБайт/с, для T-DES – 49 кБайт/с

- генератор случайных чисел по спецификации ANSI X9.82.

- поддержка различных функций обмена ключами.

Часть библиотеки (только алгоритмы шифрования T-DES, AES-128) предоставляется бесплатно в виде объектных модулей.

Библиотека несимметричных алгоритмов шифрования

Предоставляет следующие функции:

- функции шифрования-дешифрования открытого ключа RSA (1024/2048 бит).

- протокол подтверждения открытого ключа Diffie-Hellman (1024/2048 бит).

- цифровая подпись и проверка цифровой подписи DSA (1024 бит) и RSA (1024/2048 бит)

- хэш-алгоритмы SHA-1 и MD5

- генератор случайных чисел по спецификации ANSI X9.82.

Библиотеки сжатия речи

Microchip предлагает три библиотеки сжатия речи, предназначенные для использования в автоответчиках, аварийных извещателях, диктофонах и т. п.:

- CELP – платная библиотека, основанная на кодеке Speex с открытыми исходными кодами. Обеспечивает сжатие и декодирование речевого сигнала с коэффициентом 1:16 и оценкой качества PESQ = 3.7 – 4.2 (из 5.0). Может использоваться с контроллерами dsPIC30/33.

- G.711 – бесплатная библиотека, основанная на стандарте ITU-T G.711. Библиотека содержит компандер и экспандер A-law и u-law, обеспечивая сжатие с коэффициентом 1:2 и оценкой качества PESQ = 4.3 – 4.5. Может использоваться с любым контроллером 16-битного семейства.

- G.726А – платная библиотека, основанная на стандарте ITU-T G.726A (ADPCM). Обеспечивает сжатие и декодирование речевого сигнала с коэффициентами от 1:3.2 до 1:8 с оценкой качества PESQ = 4.3 – 4.5. Может использоваться с контроллерами dsPIC30/33.

Стек протоколов TCP/IP

Библиотека TCP/IP может использоваться с любым контроллером 16-битного семейства. Модульная система позволяет использовать только необходимые уровни стека и интегрировать библиотеку в уже разработанные устройства.

Поддерживаются следующие протоколы: ARP, IP, ICMP, UDP, TCP, DHCP, SNMP, HTTP, FTP, TFTP. Возможна реализация FTP и HTTP сервера на базе памяти программ или внешней памяти. Стек (без протоколов FTP и TFTP) использует не более 12 кБайт программной памяти.

Стек поддерживает 10-Base T Ethernet-контроллер ENC28J60 от Microchip. Контроллер ENC28J60 выпускается в компактном 28-выводном корпусе, содержит MAC и PHY драйверы, 8 кБайт буферной памяти, SPI интерфейс для обмена данными с хост-контроллером.

Библиотека FAT16

Бесплатная библиотека файловой системы FAT16 может использоваться с любым контроллером с 16-битной архитектурой от Microchip. Библиотека поддерживает Flash-карты памяти SD/MMC и CompacFlash. Так как библиотека поставляется в виде открытых исходных кодов, разработчик может самостоятельно добавить поддержку других устройств хранения данных.

В библиотеке реализованы стандартные функции: fopen, fread, fwrite, fseek и т. д. Для использования библиотеки требуется 16 кБайт программной памяти и 1.5 кБайт ОЗУ.

Операционные системы реального времени

Большой объем программной памяти и ОЗУ, программный стек позволяют полностью использовать все возможности операционных системам реального времени (RTOS), разрабатывая объемное приложение на контроллерах dsPIC30/33 и PIC24F/H.

Использование RTOS позволяет разделить линейный код на конечное число выполняемых параллельно задач, независимых с точки зрения программиста. Задачи могут обмениваться данными между собой используя сервисы RTOS (семафоры, сообщения, и т. п.).

Существует два вида RTOS – кооперативные (задача должна сама прерывать работу и отдавать управление системной функции переключения задач) и вытесняющие (системная функция переключения задач может завершить выполнение задачи и передать управление другой, более приоритетной задаче).

По сути RTOS – это набор функций, поставляемых в виде объектного модуля или исходных кодов, включаемых в проект. Библиотека содержит системные функции переключения задач, функции обеспечения взаимодействия между задачами, функции профилирования и т. п.

RTOS, рекомендуемая компанией Microchip для использования с 16-битными контроллерами разработана компанией CMX System. Предлагается три различных варианта:

- CMX-RTX™ - вытесняющая RTOS, поддерживающая управление задачами, событиями, системными таймерами, ресурсами задач, распределение памяти. Сервисы: семафоры, сообщения, очереди сообщений. Все функции RTOS требуют наличия 3.6 кБайт памяти программ. Каждая задача требует 28 байт ОЗУ для хранения сервисной информации.

- CMX-Tiny+™ - упрощенная версия полнофункциональной вытесняющей RTOS CMX-RTX™. Требует наличия 2.3 кБайт памяти программ. Каждая задача требует 13 байт ОЗУ для хранения сервисной информации.